- Código RS:

- 121-8582

- Nº ref. fabric.:

- DS90C365AMT/NOPB

- Fabricante:

- Texas Instruments

Temporalmente fuera de stock. Disponible a partir del 26/06/2024, con entrega en 4 día(s) laborable(s).

Añadido

Precio unitario (En un Tubo de 38)

5,561 €

(exc. IVA)

6,729 €

(inc.IVA)

| Unidades | Por unidad | Por Tubo* |

| 38 - 38 | 5,561 € | 211,318 € |

| 76 - 152 | 5,283 € | 200,754 € |

| 190 + | 5,005 € | 190,19 € |

| *precio indicativo | ||

- Código RS:

- 121-8582

- Nº ref. fabric.:

- DS90C365AMT/NOPB

- Fabricante:

- Texas Instruments

Legislación y Conformidad

- COO (País de Origen):

- US

Datos del Producto

Serializador/deserializador FlatLink/FPD-Link, Texas Instruments

Transmisores LVDS para su uso con enlaces FPD de 24 bits (display de panel plano) que funcionan a 65 y 85 MHz.

Entradas LVCMOS/LVTTL

Funcionamiento de baja potencia de 3,3 V

Reloj de datos de transmisor PLL

Cumple el estándar TIA/EIA-644 LVDS

Funcionamiento de baja potencia de 3,3 V

Reloj de datos de transmisor PLL

Cumple el estándar TIA/EIA-644 LVDS

El Texas Instruments DS90C365A es un recambio compatible contacto a contacto para DS90C363, DS90C363A y DS90C365. El DS90C365A tiene características adicionales y mejoras que lo convierten en un sustituto ideal para DS90C363, DS90C363A y DS90C365. Familia de transmisores LVDS.

Compatible contacto a contacto con DS90C363, DS90C363A y DS90C365

No se requiere una secuencia de arranque especial entre los contactos de reloj/datos y /PD. Las señales de entrada (reloj y datos) se pueden aplicar antes o después de que el dispositivo esté encendido.

Compatible con registro de amplio espectro hasta 100kHz kHz de modulación de frecuencia y desviaciones de 2,5 ±% de distribución central o 5 % de distribución descendente.

La función de “Detección de reloj de entrada” llevará todos los pares LVDS a la lógica baja cuando falta el reloj de entrada y cuando el contacto /PD está en la lógica alta.

Compatibilidad con reloj de desplazamiento de 18 a 87,5 MHz

Consumo de potencia TX < 146 mW (típ.) a 87,5 MHz Escala de grises

Modo de reducción de potencia TX < 37 uW (típ.)

Compatible con VGA, SVGA, XGA, SXGA (doble píxel), SXGA+ (doble píxel), UXGA (píxel doble).

El bus estrecho reduce el tamaño y el coste del cable

Hasta 1,785 Gbps de rendimiento

Ancho de banda de hasta 223,125 megabytes/seg

Dispositivos LVDS de oscilación de 345 mV (típ.) para EMI baja

PLL no requiere componentes externos

Conforme al estándar TIA/EIA-644 LVDS

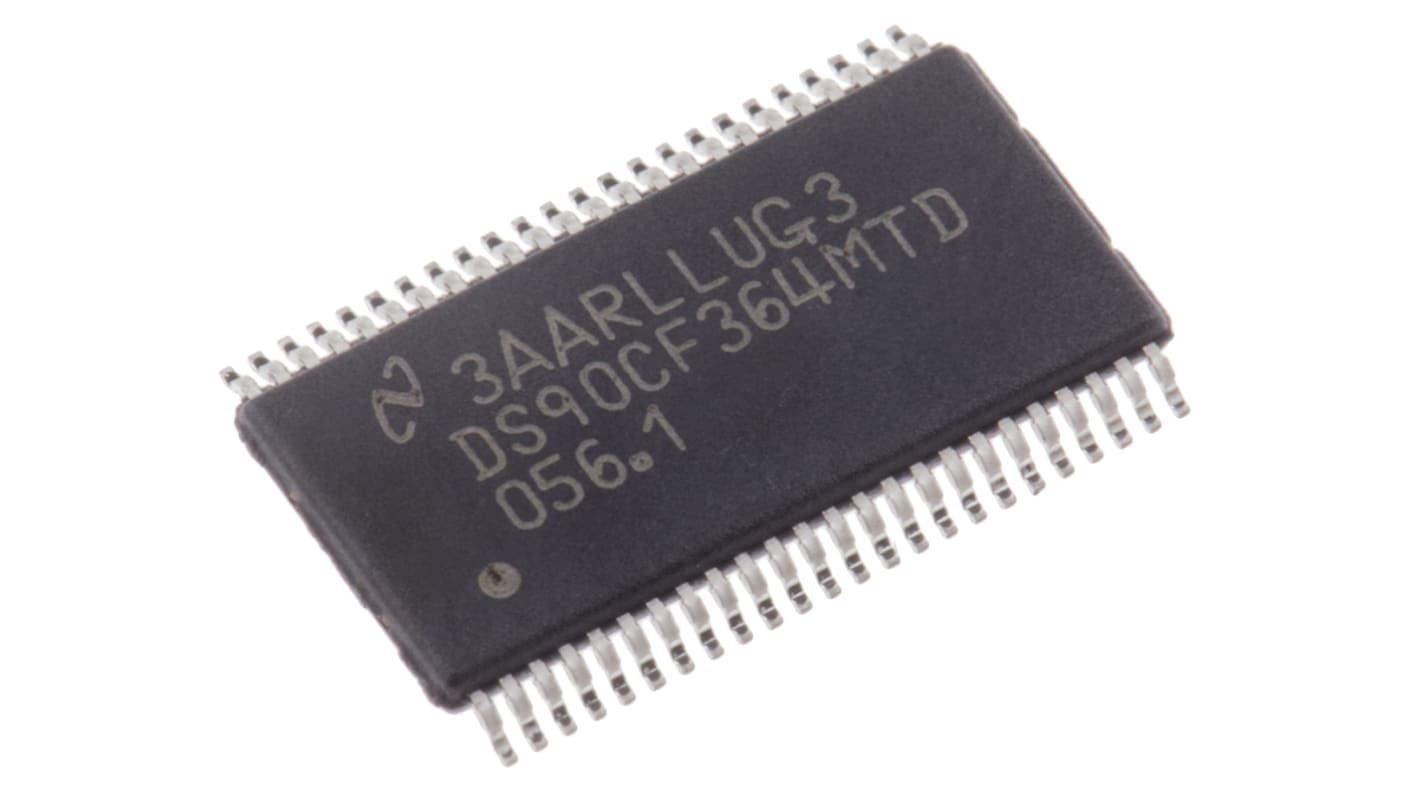

Encapsulado TSSOP de 48 cables de perfil bajo

No se requiere una secuencia de arranque especial entre los contactos de reloj/datos y /PD. Las señales de entrada (reloj y datos) se pueden aplicar antes o después de que el dispositivo esté encendido.

Compatible con registro de amplio espectro hasta 100kHz kHz de modulación de frecuencia y desviaciones de 2,5 ±% de distribución central o 5 % de distribución descendente.

La función de “Detección de reloj de entrada” llevará todos los pares LVDS a la lógica baja cuando falta el reloj de entrada y cuando el contacto /PD está en la lógica alta.

Compatibilidad con reloj de desplazamiento de 18 a 87,5 MHz

Consumo de potencia TX < 146 mW (típ.) a 87,5 MHz Escala de grises

Modo de reducción de potencia TX < 37 uW (típ.)

Compatible con VGA, SVGA, XGA, SXGA (doble píxel), SXGA+ (doble píxel), UXGA (píxel doble).

El bus estrecho reduce el tamaño y el coste del cable

Hasta 1,785 Gbps de rendimiento

Ancho de banda de hasta 223,125 megabytes/seg

Dispositivos LVDS de oscilación de 345 mV (típ.) para EMI baja

PLL no requiere componentes externos

Conforme al estándar TIA/EIA-644 LVDS

Encapsulado TSSOP de 48 cables de perfil bajo

Comunicación LVDS

La señalización de diferencial de baja tensión, o LVDS, es un sistema de señalización eléctrica que puede funcionar con velocidades muy altas sobre cables de cobre de par trenzado.

Aplicaciones: Firewire, SATA, SCSI

Especificaciones

Atributo | Valor |

|---|---|

| Número de Drivers | 3 |

| Tipo de Salida | Display de panel frontal |

| Interfaz | Circuito integrado del transceptor |

| Índice de Transmisión de Datos | 612.5Mbps |

| Número de Elementos por Chip | 3 |

| Tipo de Montaje | Montaje superficial |

| Tipo de Encapsulado | TSSOP |

| Conteo de Pines | 48 |

| Dimensiones | 12.5 x 6.1 x 0.9mm |

| Altura | 0.9mm |

| Longitud | 12.5mm |

| Tensión de Alimentación Máxima de Funcionamiento | 3,6 V |

| Temperatura de Funcionamiento Mínima | -10 °C |

| Temperatura Máxima de Funcionamiento | +70 °C |

| Tensión de Alimentación de Funcionamiento Mínima | 3 V |

| Ancho | 6.1mm |

- Código RS:

- 121-8582

- Nº ref. fabric.:

- DS90C365AMT/NOPB

- Fabricante:

- Texas Instruments

- COO (País de Origen):

- US

Enlaces relacionados

- Transceptor LVDS Dual LVDS Controlador 100Mbps 14-Pines

- Transceptor LVDS Quad TSSOP, 20-Pines

- Transceptor LVDS LVCMOS MLVDS 200Mbps 8-Pines

- Transceptor LVDS Dual LVTTL receptor TSSOP, 16-Pines

- Transceptor LVDS 3 Display de panel frontal TSSOP, 48-Pines

- Transceptor LVDS 8, CMOS

- Transceptor LVDS 125Mbps 20-Pines

- Transceptor LVDS LVCMOS LVTTL 100Mbps 8-Pines