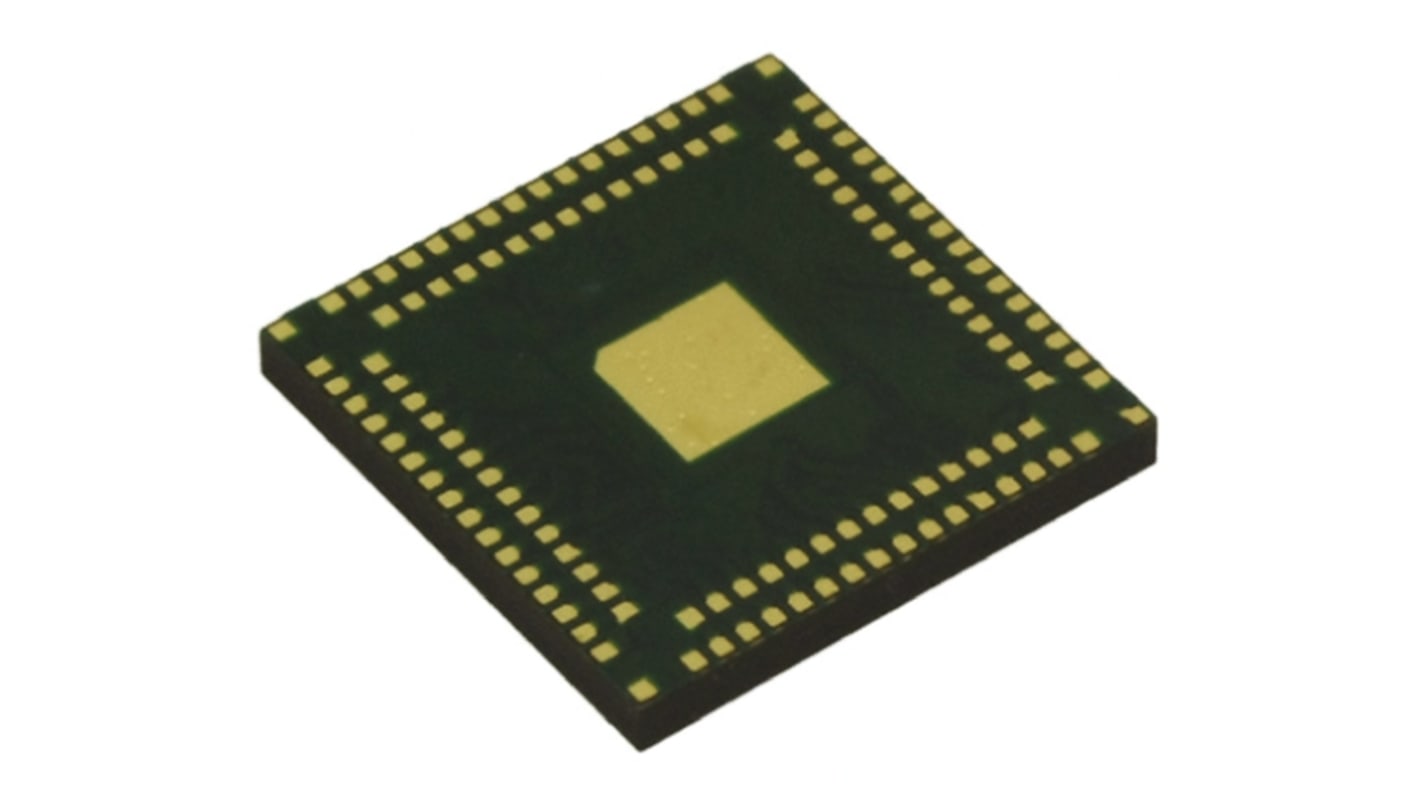

Microcontrolador XMOS, núcleo Multi-núcleo, 128 kB RAM, 128kB, 60 MHz, QFN Flash de 124 pines

- Código RS:

- 170-0886

- Nº ref. fabric.:

- XS1-L02A-QF124-C5

- Fabricante:

- XMOS

Subtotal (1 bandeja de 168 unidades)*

4.967,424 €

(exc. IVA)

6.010,536 €

(inc.IVA)

Entrega GRATUITA para pedidos superiores a 95,00 €

Agotado temporalmente

- Envío desde el 01 de septiembre de 2026

¿Necesitas comprar más? Introduce la nueva cantidad y clica en "Consultar fechas de entrega"

Unidad(es) | Por unidad | Por Bandeja* |

|---|---|---|

| 168 + | 29,568 € | 4.967,42 € |

*precio indicativo

- Código RS:

- 170-0886

- Nº ref. fabric.:

- XS1-L02A-QF124-C5

- Fabricante:

- XMOS

Especificaciones

Documentación Técnica

Legislación y Conformidad

Datos del Producto

Encuentra productos similares seleccionando uno o varios atributos.

Seleccionar todo | Atributo | Valor |

|---|---|---|

| Marca | XMOS | |

| Serie | XS1 | |

| Tipo de producto | Microcontrolador | |

| Encapsulado | QFN | |

| Tipo de montaje | Superficie | |

| Número de pines | 124 | |

| Núcleo del dispositivo | Multi-núcleo | |

| Tamaño de la memoria de programa | 128kB | |

| Tipo de interfaz | JTAG, SPI | |

| Frecuencia del reloj máxima | 60MHZ | |

| Tamaño RAM | 128kB | |

| Tensión de alimentación máxima | 3.6V | |

| Disipación de potencia máxima Pd | 450W | |

| Número de E/S programables | 84 | |

| Temperatura de Funcionamiento Mínima | -40°C | |

| Temperatura de funcionamiento máxima | 85°C | |

| Longitud | 10mm | |

| Altura | 1.11mm | |

| Certificaciones y estándares | REACH, RoHS3 | |

| Tensión de alimentación mínima | 3V | |

| Arquitectura del juego de instrucciones | RISC | |

| Estándar de automoción | No | |

| Tipo de memoria de programa | Flash | |

| Seleccionar todo | ||

|---|---|---|

Marca XMOS | ||

Serie XS1 | ||

Tipo de producto Microcontrolador | ||

Encapsulado QFN | ||

Tipo de montaje Superficie | ||

Número de pines 124 | ||

Núcleo del dispositivo Multi-núcleo | ||

Tamaño de la memoria de programa 128kB | ||

Tipo de interfaz JTAG, SPI | ||

Frecuencia del reloj máxima 60MHZ | ||

Tamaño RAM 128kB | ||

Tensión de alimentación máxima 3.6V | ||

Disipación de potencia máxima Pd 450W | ||

Número de E/S programables 84 | ||

Temperatura de Funcionamiento Mínima -40°C | ||

Temperatura de funcionamiento máxima 85°C | ||

Longitud 10mm | ||

Altura 1.11mm | ||

Certificaciones y estándares REACH, RoHS3 | ||

Tensión de alimentación mínima 3V | ||

Arquitectura del juego de instrucciones RISC | ||

Estándar de automoción No | ||

Tipo de memoria de programa Flash | ||

- COO (País de Origen):

- SG

Procesador controlado por eventos XS1

Un XS1 combina una serie de procesadores XCore™, cada uno con su propia memoria, en un único chip. Los procesadores programables son de uso general en el sentido que pueden ejecutar lenguajes como C; también tienen soporte directo para procesamiento concurrente (multitrama) comunicación y entrada-salida. Un conmutador de gran rendimiento mantiene la comunicación entre los procesadores, y XMOS Links inter-chip se facilitan para que los sistemas puedan construirse fácilmente desde múltiples chips. Los productos XS1 se han pensado para que el uso de software sea práctico para realizar muchas funcionas que normalmente se realizarían mediante hardware; un ejemplo importante se refleja en interfaces y controladores de entrada-salida.

Cada procesador XCore proporciona los siguientes recursos:

Procesador de 32 bits que proporciona hasta 500 MIPS

Ocho tramas de hardware y 32 extremos de canal

Diez temporizadores y seis bloques de reloj

Cuatro XMOS Link

SRAM de 64 KBytes y memoria OTP de 8K Bytes

El XCore es un componente de procesamiento de varios procesos con compatibilidad de instrucciones para comunicación, entrada-salida y temporización. La ejecución de procesos es determinista y el tiempo que se tarda en ejecutar una serie de instrucciones puede predecirse de manera precisa. Esto permite al software que se ejecuta en un XCore realizar muchas funciones normalmente realizadas por hardware, especialmente DSP y E/S. Cada proceso de XCore tiene un conjunto dedicado de registros y la programación de procesos la realiza el hardware. La comunicación entre procesos se realiza usando canales de hardware. Las instrucciones de comunicación transfieren los datos directamente entre registros de procesador y canales, programando y desprogramando automáticamente los procesos de comunicación para controlar el flujo de datos. El XCore tiene un conjunto de instrucciones eficaz para admitir lenguajes de programación secuenciales convencionales. Sus instrucciones de entrada-salida, comunicación y varios procesos están diseñadas para admitir lenguajes de programación modernos. El conjunto de instrucciones es fácilmente extensible para proporcionar instrucciones específicas de aplicaciones; estas incluyen actualmente compatibilidad aritmética, CRC, DSP y criptografía. Cada XCore tiene un sistema de memoria unificado que comparten para programas y datos todos los procesos ejecutados por el núcleo. Varios procesos pueden compartir el mismo programa en la memoria y pueden pasar la propiedad de datos entre ellos. No se utiliza caché. El XCore tiene un conjunto integrado de puertos de E/S controlados directamente por instrucciones. Los datos se transfieren directamente entre registros de procesador y puertos, evitando el uso de memoria y minimizando la latencia. Los puertos pueden serializar y deserializar datos permitiendo al procesador controlar flujos de datos de alta velocidad. También pueden marcar con tiempo la llegada de datos y controlar de manera precisa la hora a la que se transfirieron los datos hacia o desde los contactos.

Enlaces relacionados

- Microcontrolador XMOS 128 kB RAM 60 MHz, QFN Flash de 124 pines

- Microcontrolador XMOS XS1-L02A-QF124-C5 128 kB RAM 60 MHz, QFN Flash de 124 pines

- Microcontrolador XMOS XS1-L01A-TQ128-C5 64 kB RAM TQFP Flash de 128 pines

- Microcontrolador MCU XMOS XS1-L01A-TQ128-C5

- Microcontrolador Microchip 4 bit RAM QFN Flash de 28 pines

- Microcontrolador Microchip 1 bit RAM QFN Flash de 64 pines

- Microcontrolador Microchip PIC18F27K40-E/ML 4 bit RAM QFN Flash de 28 pines

- Microcontrolador Microchip PIC18F67K22-E/MR 1 bit RAM QFN Flash de 64 pines