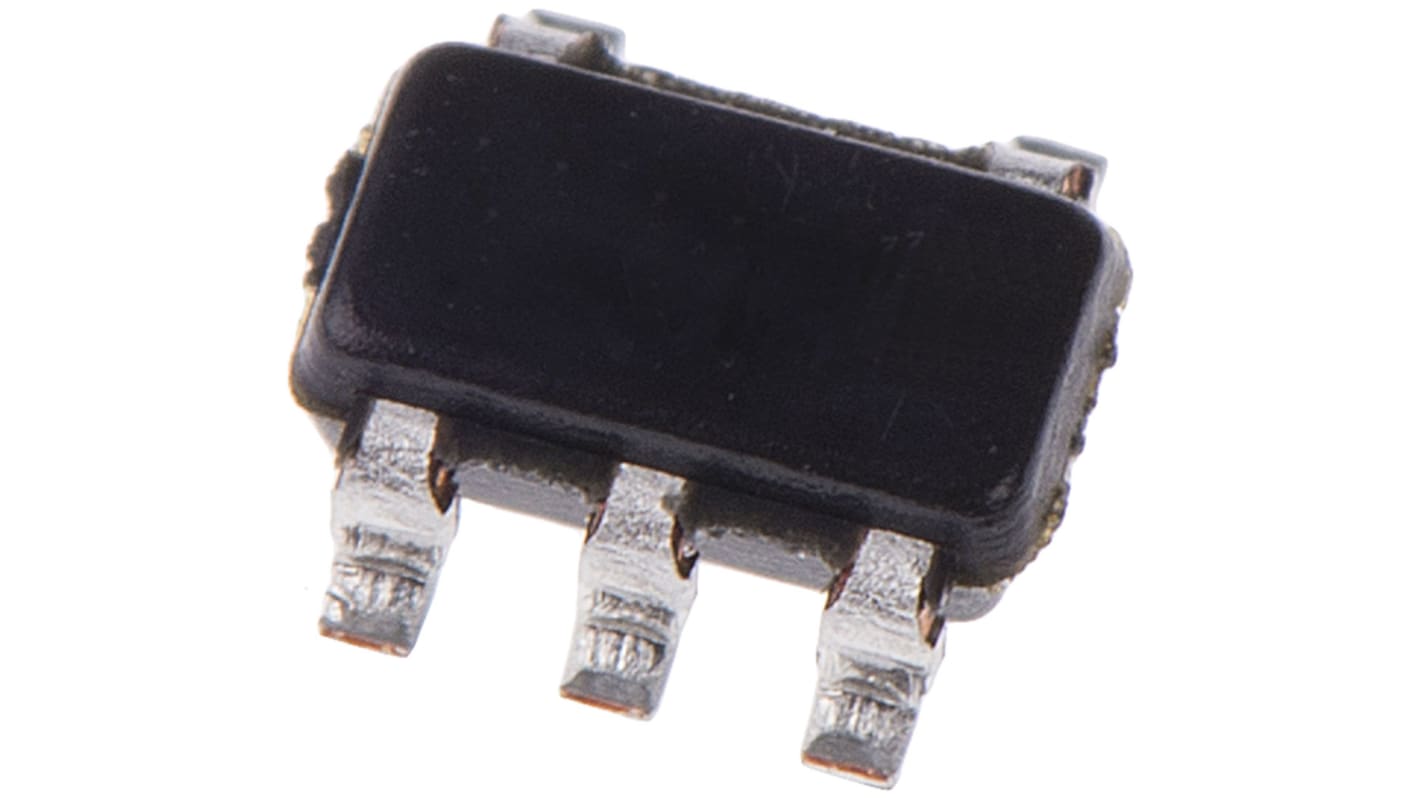

Texas Instruments Búfer SN74LVC1G126DBVR 74LVC 1 canales 3 estados Búfer No Inversión SOT-23 5 pines

- Código RS:

- 796-8240

- Nº ref. fabric.:

- SN74LVC1G126DBVR

- Fabricante:

- Texas Instruments

Descuento aplicable por cantidad

Subtotal (1 paquete de 25 unidades)*

2,025 €

(exc. IVA)

2,45 €

(inc.IVA)

Información relativa a las existencias no accesible actualmente - Vuelva a comprobarlo más tarde

Unidad(es) | Por unidad | Por Paquete* |

|---|---|---|

| 25 - 100 | 0,081 € | 2,03 € |

| 125 - 225 | 0,077 € | 1,93 € |

| 250 - 600 | 0,07 € | 1,75 € |

| 625 - 1225 | 0,062 € | 1,55 € |

| 1250 + | 0,06 € | 1,50 € |

*precio indicativo

- Código RS:

- 796-8240

- Nº ref. fabric.:

- SN74LVC1G126DBVR

- Fabricante:

- Texas Instruments

Especificaciones

Documentación Técnica

Legislación y Conformidad

Datos del Producto

Encuentra productos similares seleccionando uno o varios atributos.

Seleccionar todo | Atributo | Valor |

|---|---|---|

| Marca | Texas Instruments | |

| Tipo de producto | Búfer | |

| Familia lógica | 74LVC | |

| Función lógica | Búfer | |

| Número de canales | 1 | |

| Entrada Schmitt Trigger | No | |

| Tipo de entrada | TTL, CMOS | |

| Tipo de salida | 3 estados | |

| Tipo de montaje | Superficie | |

| Polaridad | No Inversión | |

| Encapsulado | SOT-23 | |

| Tensión de alimentación mínima | 1.65V | |

| Número de pines | 5 | |

| Tensión de alimentación máxima | 5.5V | |

| Corriente máxima de salida de nivel alto | -32mA | |

| Temperatura de Funcionamiento Mínima | -40°C | |

| Temperatura de funcionamiento máxima | 125°C | |

| Corriente máxima de salida de nivel bajo | 32mA | |

| Altura | 1.3mm | |

| Longitud | 3.05mm | |

| Certificaciones y estándares | RoHS | |

| Serie | SN74LVC1G126 | |

| Estándar de automoción | No | |

| Seleccionar todo | ||

|---|---|---|

Marca Texas Instruments | ||

Tipo de producto Búfer | ||

Familia lógica 74LVC | ||

Función lógica Búfer | ||

Número de canales 1 | ||

Entrada Schmitt Trigger No | ||

Tipo de entrada TTL, CMOS | ||

Tipo de salida 3 estados | ||

Tipo de montaje Superficie | ||

Polaridad No Inversión | ||

Encapsulado SOT-23 | ||

Tensión de alimentación mínima 1.65V | ||

Número de pines 5 | ||

Tensión de alimentación máxima 5.5V | ||

Corriente máxima de salida de nivel alto -32mA | ||

Temperatura de Funcionamiento Mínima -40°C | ||

Temperatura de funcionamiento máxima 125°C | ||

Corriente máxima de salida de nivel bajo 32mA | ||

Altura 1.3mm | ||

Longitud 3.05mm | ||

Certificaciones y estándares RoHS | ||

Serie SN74LVC1G126 | ||

Estándar de automoción No | ||

Búferes e inversores de la familia 74LVC, Texas Instruments

Gama de inversores y búferes de la familia 74LVC de los CI de lógica CMOS de baja tensión de Texas Instruments La familia 74LVC utiliza tecnología CMOS de puerta de silicio y está diseñada para funcionar a 3,3 V, lo que permite una reducción significativa del consumo de energía en comparación con los sistemas de 5 V.

Tensión de funcionamiento: 1,65 a 3,6 V

Entradas tolerantes de 5 V

Compatibilidad: entrada LVTTL/TTL, salida LVCMOS

El rendimiento de cierre excede 250 mA conforme a JESD 17

La protección contra ESD excede JESD 22

Familia 74LVC

Enlaces relacionados

- Texas Instruments Búfer 74LVC 1 canales 3 estados Búfer No Inversión SOT-23 5 pines

- Texas Instruments Búfer 74LVC 1 canales CMOS Búfer SOT-23 5 pines

- Texas Instruments Búfer SN74LVC1G34DBVR 74LVC 1 canales CMOS Búfer SOT-23 5 pines

- Texas Instruments AEC-Q100 Búfer, Controlador Driver de búfer/línea 74LVC 1 bits Drenador abierto No Inversión SOT-23 5

- Texas Instruments Búfer SN74LVC2G34DBVT 74LVC 2 canales Búfer Driver doble de búfer/línea Positivo SOT-23 6 pines

- Texas Instruments Búfer AHC CMOS Búfer de bus No Inversión SOT-23 5 pines

- Texas Instruments Controlador

- Texas Instruments Búfer SN74AHC1G125DBVR AHC CMOS Búfer de bus No Inversión SOT-23 5 pines