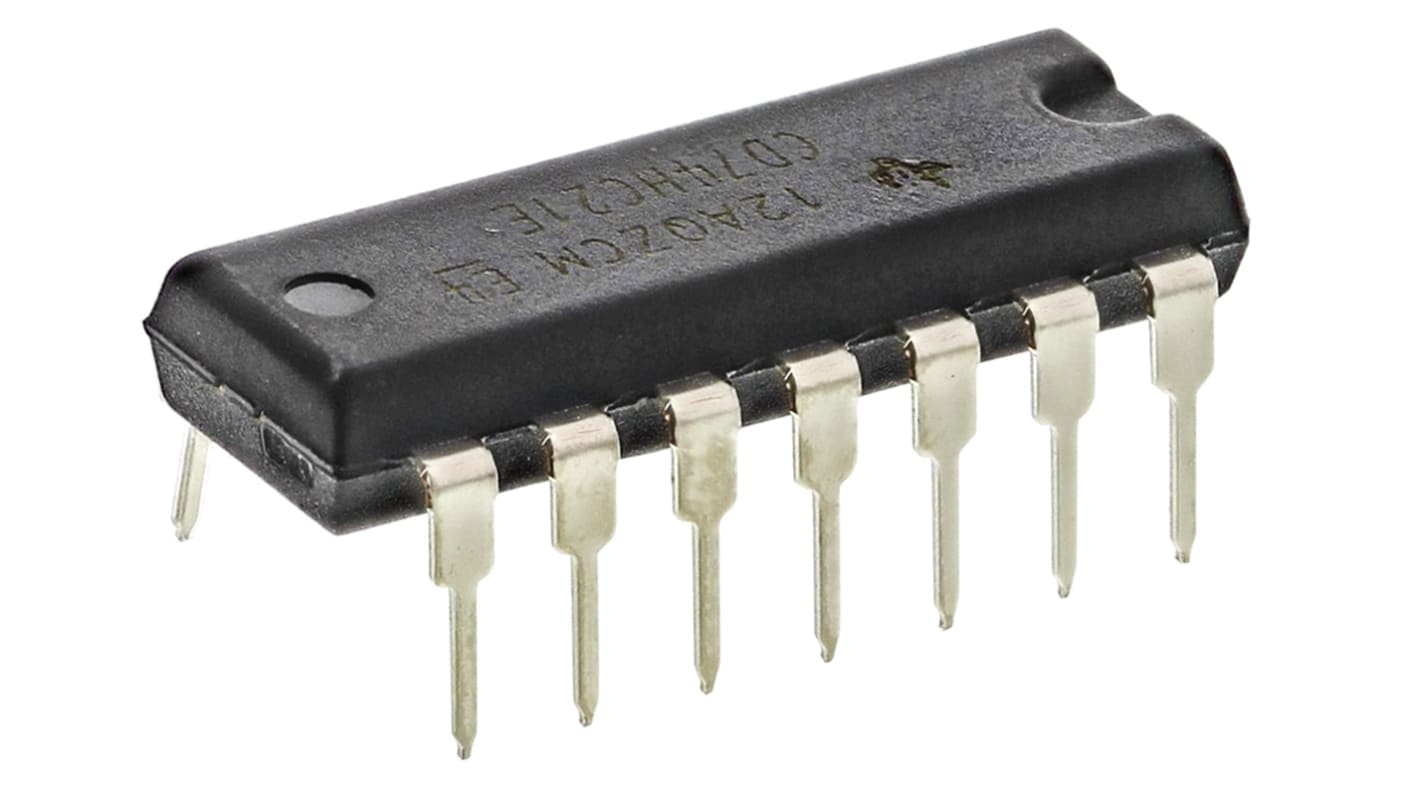

Y: Puerta lógica, CD74HC21E, HC, Dual 5.2mA PDIP 14 pines 4 No

- Código RS:

- 145-0150

- Nº ref. fabric.:

- CD74HC21E

- Fabricante:

- Texas Instruments

No disponible

RS ya no dispondrá de este producto.

- Código RS:

- 145-0150

- Nº ref. fabric.:

- CD74HC21E

- Fabricante:

- Texas Instruments

Especificaciones

Documentación Técnica

Legislación y Conformidad

Encuentra productos similares seleccionando uno o varios atributos.

Seleccionar todo | Atributo | Valor |

|---|---|---|

| Marca | Texas Instruments | |

| Función Lógica | Y | |

| Tipo de Montaje | Montaje en orificio pasante | |

| Número de Elementos | 2 | |

| Number of Inputs per Gate | 4 | |

| Entrada de disparador Schmitt | No | |

| Tipo de Encapsulado | PDIP | |

| Conteo de Pines | 14 | |

| Familia Lógica | HC | |

| Tensión de Alimentación Máxima de Funcionamiento | 6 V | |

| Corriente Máxima de Salida de Alto Nivel | -5.2mA | |

| Tipo de Retardo de Propagación Máxima @ CL Máximo | 110 ns @ 2 V, 19 ns @ 6 V, 22 ns @ 4.5 V | |

| Tensión de Alimentación de Funcionamiento Mínima | 2 V | |

| Corriente Máxima de Salida de Bajo Nivel | 5.2mA | |

| Ancho | 6.35mm | |

| Temperatura de Funcionamiento Mínima | -55 °C | |

| Altura | 4.57mm | |

| Condición de Prueba de Retardo de Propagación | 50pF | |

| Temperatura Máxima de Funcionamiento | +125 °C | |

| Longitud | 19.3mm | |

| Dimensiones | 19.3 x 6.35 x 4.57mm | |

| Seleccionar todo | ||

|---|---|---|

Marca Texas Instruments | ||

Función Lógica Y | ||

Tipo de Montaje Montaje en orificio pasante | ||

Número de Elementos 2 | ||

Number of Inputs per Gate 4 | ||

Entrada de disparador Schmitt No | ||

Tipo de Encapsulado PDIP | ||

Conteo de Pines 14 | ||

Familia Lógica HC | ||

Tensión de Alimentación Máxima de Funcionamiento 6 V | ||

Corriente Máxima de Salida de Alto Nivel -5.2mA | ||

Tipo de Retardo de Propagación Máxima @ CL Máximo 110 ns @ 2 V, 19 ns @ 6 V, 22 ns @ 4.5 V | ||

Tensión de Alimentación de Funcionamiento Mínima 2 V | ||

Corriente Máxima de Salida de Bajo Nivel 5.2mA | ||

Ancho 6.35mm | ||

Temperatura de Funcionamiento Mínima -55 °C | ||

Altura 4.57mm | ||

Condición de Prueba de Retardo de Propagación 50pF | ||

Temperatura Máxima de Funcionamiento +125 °C | ||

Longitud 19.3mm | ||

Dimensiones 19.3 x 6.35 x 4.57mm | ||

- COO (País de Origen):

- MY

Enlaces relacionados

- NOR: Puerta lógica HC, Dual 5.2mA PDIP 14 pines 4 No

- NAND: Puerta lógica HC, Dual 5.2mA PDIP 14 pines 4 No

- Y: Puerta lógica HC, Dual 5.2mA SOIC 14 pines 4 No

- NAND: Puerta lógica HC, Dual 5.2mA SOIC 14 pines 4 No

- NOR: Puerta lógica HC, Dual 5.2mA SOIC 14 pines 4 No

- O: Puerta lógica HC, Triple 5.2mA PDIP 14 pines 3 No

- NOR: Puerta lógica HC, Triple 5.2mA PDIP 14 pines 3 No

- XNOR: Puerta lógica HC, Drenaje Abierto Quad 5.2mA PDIP 14 pines 2 No