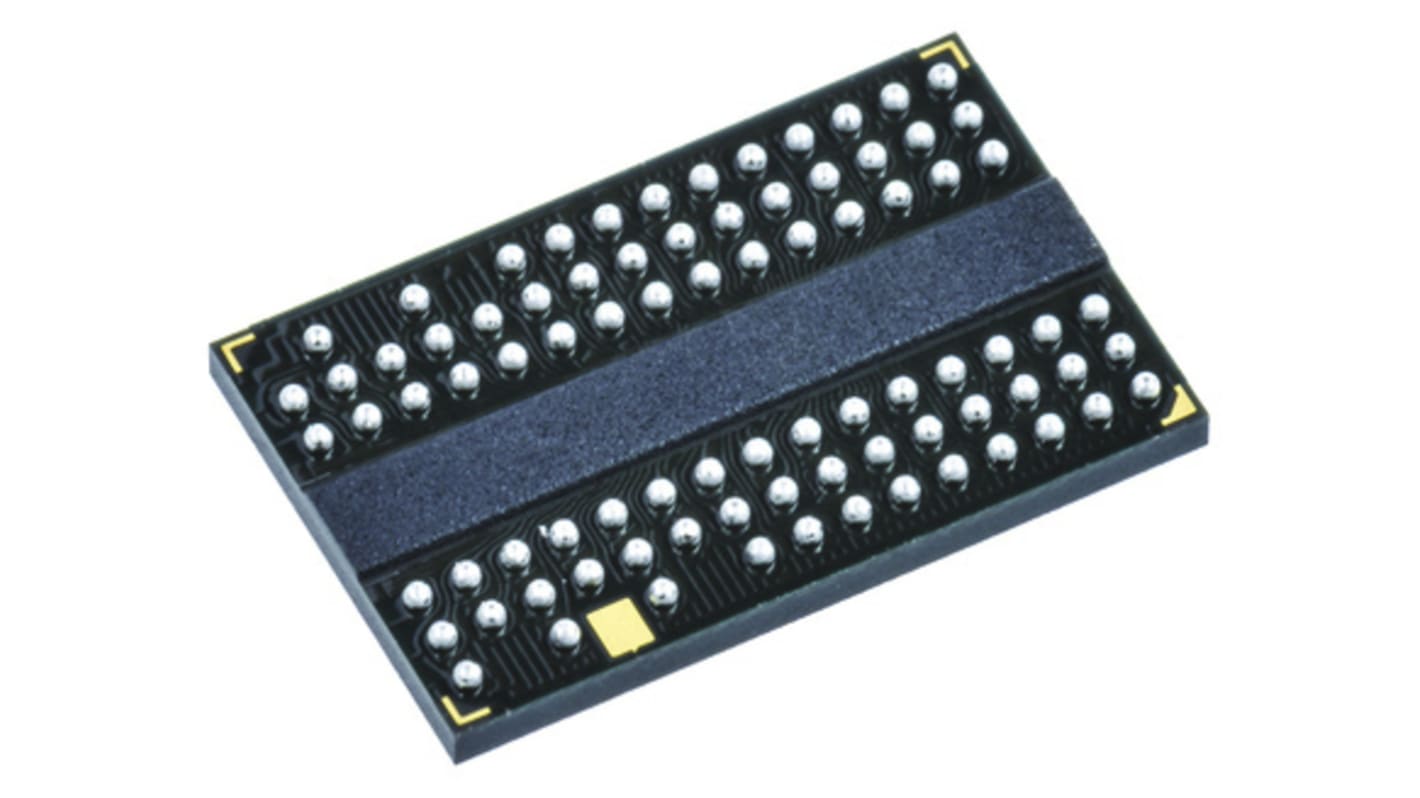

Memoria DDR2 SDRAM W9725G6KB-25/TRAY, 256Mbit, 800MHZ, Montaje superficial, WBGA, 84 pines DDR2

- Código RS:

- 171-2246P

- Nº ref. fabric.:

- W9725G6KB-25/TRAY

- Fabricante:

- Winbond

Disponibilidad de stock no accesible

- Código RS:

- 171-2246P

- Nº ref. fabric.:

- W9725G6KB-25/TRAY

- Fabricante:

- Winbond

Especificaciones

Documentación Técnica

Legislación y Conformidad

Datos del Producto

Encuentra productos similares seleccionando uno o varios atributos.

Seleccionar todo | Atributo | Valor |

|---|---|---|

| Marca | Winbond | |

| Tamaño de la Memoria | 256Mbit | |

| Clase SDRAM | DDR2 | |

| Organización | 16 M x 16 bits | |

| Transmisión de Datos | 800MHZ | |

| Ancho del Bus de Datos | 16bit | |

| Ancho del Bus de Direcciones | 16bit | |

| Número de Bits de Palabra | 16M | |

| Número de Palabras | 16M | |

| Tipo de Montaje | Montaje superficial | |

| Tipo de Encapsulado | WBGA | |

| Conteo de Pines | 84 | |

| Dimensiones | 8.1 x 12.6 x 0.8mm | |

| Altura | 0.8mm | |

| Longitud | 8.1mm | |

| Tensión de Alimentación Máxima de Funcionamiento | 1,9 V | |

| Ancho | 12.6mm | |

| Temperatura Máxima de Funcionamiento | +85 °C | |

| Temperatura de Funcionamiento Mínima | 0 °C | |

| Tensión de Alimentación de Funcionamiento Mínima | 1,7 V | |

| Seleccionar todo | ||

|---|---|---|

Marca Winbond | ||

Tamaño de la Memoria 256Mbit | ||

Clase SDRAM DDR2 | ||

Organización 16 M x 16 bits | ||

Transmisión de Datos 800MHZ | ||

Ancho del Bus de Datos 16bit | ||

Ancho del Bus de Direcciones 16bit | ||

Número de Bits de Palabra 16M | ||

Número de Palabras 16M | ||

Tipo de Montaje Montaje superficial | ||

Tipo de Encapsulado WBGA | ||

Conteo de Pines 84 | ||

Dimensiones 8.1 x 12.6 x 0.8mm | ||

Altura 0.8mm | ||

Longitud 8.1mm | ||

Tensión de Alimentación Máxima de Funcionamiento 1,9 V | ||

Ancho 12.6mm | ||

Temperatura Máxima de Funcionamiento +85 °C | ||

Temperatura de Funcionamiento Mínima 0 °C | ||

Tensión de Alimentación de Funcionamiento Mínima 1,7 V | ||

El W9725G6KB es una SDRAM DDR2 de 256M bits con una velocidad de -18, -25, 25I y -3

Arquitectura de doble velocidad de datos: dos transferencias de datos por ciclo de reloj

Latencia CAS: 3, 4, 5, 6 y 7

Longitud de ráfaga: 4 y 8

Las señales intermitentes de datos diferenciales (DQS y /DQS) bidireccionales se transmiten o reciben con datos.

Alineación de borde y centro y datos de lectura alineados con datos de escritura

El DLL alinea las transiciones DQ y DQS con el reloj

Entradas de reloj diferencial (CLK y /CLK)

Máscaras de datos (DM) para escribir datos

Ajuste de impedancia de controlador de chip de desconexión (OCD) y terminación en matriz (ODT) para mejor calidad de señal

Funcionamiento precarga automático para ráfagas de lectura y escritura

Actualización automática y modos de actualización automática

Desconexión con precarga y desconexión activa

Latencia CAS: 3, 4, 5, 6 y 7

Longitud de ráfaga: 4 y 8

Las señales intermitentes de datos diferenciales (DQS y /DQS) bidireccionales se transmiten o reciben con datos.

Alineación de borde y centro y datos de lectura alineados con datos de escritura

El DLL alinea las transiciones DQ y DQS con el reloj

Entradas de reloj diferencial (CLK y /CLK)

Máscaras de datos (DM) para escribir datos

Ajuste de impedancia de controlador de chip de desconexión (OCD) y terminación en matriz (ODT) para mejor calidad de señal

Funcionamiento precarga automático para ráfagas de lectura y escritura

Actualización automática y modos de actualización automática

Desconexión con precarga y desconexión activa

Enlaces relacionados

- Winbond SDRAM W972GG6KB25I Superficie WBGA 16 bit, 84 pines

- Winbond SDRAM DDR2 Superficie 84 pines

- Winbond SDRAM DDR2 W9712G6KB25I Superficie 84 pines

- SDRAM IS42S32800D-7TL 143MHZ TSOP, 86 pines

- Chip DDR SDRAM W94AD6KBHX5I/TRAY DDR VFBGA, 60 pines DDR

- Intelligent Memory SDRAM IM1G16D2DDBG-25 Superficie 84 pines

- Intelligent Memory SDRAM IM5116D2DDBG-25I Superficie 84 pines

- Intelligent Memory SDRAM IM5116D2DDBG-25 Superficie 84 pines