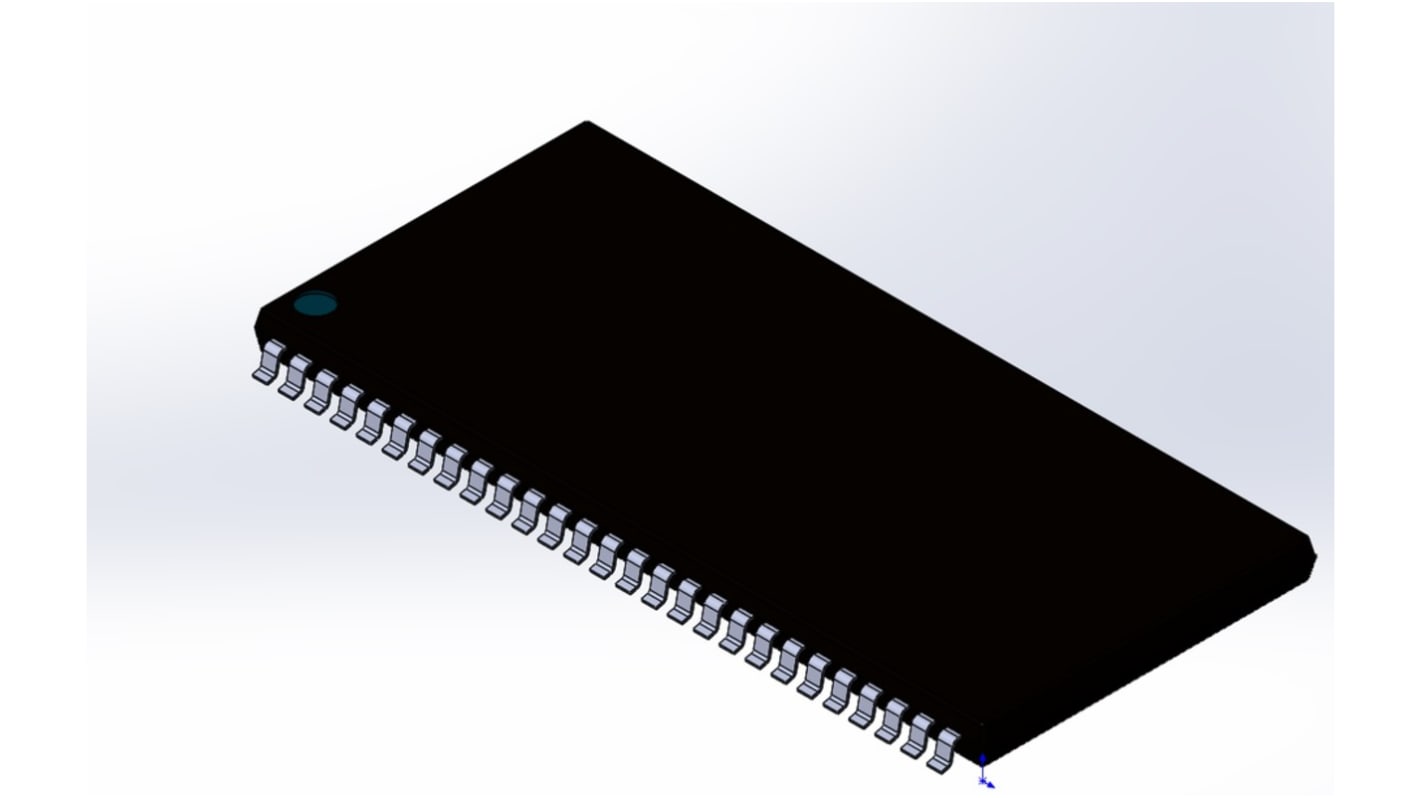

Alliance Memory SDRAM AS4C8M16SA-7TCN, 128 MB, Superficie, TSOP 16 bit, 54 pines

- Código RS:

- 230-8442

- Número de artículo Distrelec:

- 304-31-281

- Nº ref. fabric.:

- AS4C8M16SA-7TCN

- Fabricante:

- Alliance Memory

Descuento aplicable por cantidad

Subtotal (1 paquete de 2 unidades)*

5,64 €

(exc. IVA)

6,82 €

(inc.IVA)

Entrega GRATUITA para pedidos superiores a 95,00 €

Disponible

- Disponible(s) 6 unidad(es) más para enviar a partir del 11 de mayo de 2026

¿Necesitas comprar más? Introduce la nueva cantidad y clica en "Consultar fechas de entrega"

Unidad(es) | Por unidad | Por Paquete* |

|---|---|---|

| 2 - 8 | 2,82 € | 5,64 € |

| 10 - 18 | 2,53 € | 5,06 € |

| 20 - 48 | 2,49 € | 4,98 € |

| 50 - 98 | 2,43 € | 4,86 € |

| 100 + | 2,225 € | 4,45 € |

*precio indicativo

- Código RS:

- 230-8442

- Número de artículo Distrelec:

- 304-31-281

- Nº ref. fabric.:

- AS4C8M16SA-7TCN

- Fabricante:

- Alliance Memory

Especificaciones

Documentación Técnica

Legislación y Conformidad

Datos del Producto

Encuentra productos similares seleccionando uno o varios atributos.

Seleccionar todo | Atributo | Valor |

|---|---|---|

| Marca | Alliance Memory | |

| Tipo de producto | SDRAM | |

| Tamaño de la memoria | 128MB | |

| Ancho del bus de datos | 16bit | |

| Número de líneas de bus | 12bit | |

| Frecuencia del reloj máxima | 143MHZ | |

| Número de bits por palabra | 16 | |

| Tiempo de acceso aleatorio máximo | 5.4ns | |

| Número de palabras | 2M | |

| Tipo de montaje | Superficie | |

| Encapsulado | TSOP | |

| Número de pines | 54 | |

| Temperatura de Funcionamiento Mínima | 0°C | |

| Temperatura de funcionamiento máxima | 70°C | |

| Altura | 1.2mm | |

| Certificaciones y estándares | No | |

| Longitud | 22.35mm | |

| Serie | AS4C8M16SA | |

| Tensión de alimentación mínima | 3V | |

| Tensión de alimentación máxima | 3.6V | |

| Estándar de automoción | No | |

| Seleccionar todo | ||

|---|---|---|

Marca Alliance Memory | ||

Tipo de producto SDRAM | ||

Tamaño de la memoria 128MB | ||

Ancho del bus de datos 16bit | ||

Número de líneas de bus 12bit | ||

Frecuencia del reloj máxima 143MHZ | ||

Número de bits por palabra 16 | ||

Tiempo de acceso aleatorio máximo 5.4ns | ||

Número de palabras 2M | ||

Tipo de montaje Superficie | ||

Encapsulado TSOP | ||

Número de pines 54 | ||

Temperatura de Funcionamiento Mínima 0°C | ||

Temperatura de funcionamiento máxima 70°C | ||

Altura 1.2mm | ||

Certificaciones y estándares No | ||

Longitud 22.35mm | ||

Serie AS4C8M16SA | ||

Tensión de alimentación mínima 3V | ||

Tensión de alimentación máxima 3.6V | ||

Estándar de automoción No | ||

La SDRAM Alliance Memory 128MB es una DRAM síncrona CMOS de alta velocidad que contiene 128 Mbits. Está configurado internamente como 4 bancos de 16 canal x 2M DRAM con una interfaz síncrona (todas las señales se registran en el borde positivo de la señal de reloj, CLK). Los accesos de lectura y escritura a la SDRAM están orientados a ráfagas; los accesos comienzan en una ubicación seleccionada y continúan durante un número programado de ubicaciones en una secuencia programada. Los accesos comienzan con el registro de un comando BankActivate, seguido por un comando Read o Write.

Actualización automática y actualización automática

4096 ciclos de actualización/64ms

Modo de desconexión CKE

Fuente de alimentación única de +3,3V 0,3V V.

Interfaz: LVTTL

Enlaces relacionados

- Alliance Memory SDRAM Superficie 54 pines

- Alliance Memory SDRAM AS4C8M16SA-6TIN Superficie 54 pines

- Alliance Memory SDRAM AS4C8M16SA-7TCNTR Superficie 54 pines

- Alliance Memory SDRAM AS4C4M16SA-7TCN Superficie 54 pines

- Alliance Memory SDRAM AS4C32M16SB-7TCN Superficie 54 pines

- Alliance Memory SDRAM AS4C16M16SA-7TCN Superficie 54 pines

- Alliance Memory SDRAM Superficie 54 pines

- Alliance Memory SDRAM Superficie 54 pines